# Macromodeling and Multi-GHz Interconnection Simulation

Asian IBIS Summit

Zhu ShunLin

High-Speed System Lab, ZTE Corporation

Zhu.shunlin@zte.com.cn

December 2005

# Agenda

- Transistor-Level Model versus Behavior-level Model

- Macromodeling of Complex IOs

- Lab Correlation for Macromodels

- Multi-GHz System Interconnect Simulation

- Conclusions

#### Transistor-level model and Behavior-level model

#### **∨** SPICE Model

- Ø Good accuracy

- models are derived from transistor-level netlist and layout

- Ø Relatively long simulation time and sometimes convergence problems

- Intellectual property protection concerns

#### **v** IBIS Model

- Ø Models are derived from measurements and/or full SPICE model simulations

- Ø Fast simulation run time

- Ø Model must be verified, sometimes be converted and modified before usage

- Ø Difficult in Modeling complex transceiver buffers

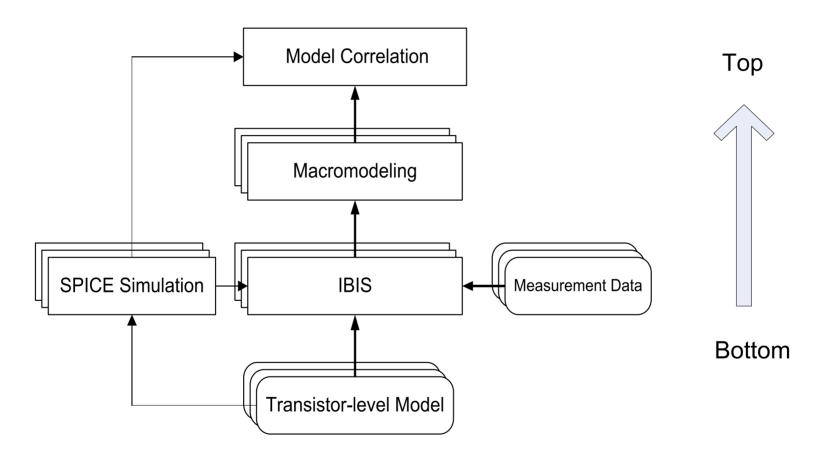

#### V MacroModel

- Ø Fast simulation run time

- A simply modeling solution for complex IOs, such as pre-emphasis buffers

- Ø Macromodel is based on IBIS model

### Modeling methodology

- Modeling is quite involved, it covers active devices as well as passive devices, such as package, transmission line, connector, via, and plane etc..

- Not all modeling methods are the same. They have tradeoffs and are suitable for different applications.

- There are behavioral IBIS and structural Spice modeling for active devices. Spice model is appropriate for demanding situations, while IBIS model is often used in system and board level simulation.

- Circuit simulators can run both IBIS and Spice. Different simulators have different characteristics.

### Modeling of complex IOs

- ✓ IBIS Multi-lingual Modeling

- Ø VHDL-AMS

- Ø Verilog-AMS

- Incorporating SPICE Subcircuits

- Incorporating External Model

- Incorporating S-Parameter Model

- Macromodeling based on IBIS

- A simply solution for complex buffers

- Combining spice subcircuits and behavioral models

# Macromodeling and its correlation flow

For behavior-level modeling, correlation is necessary.

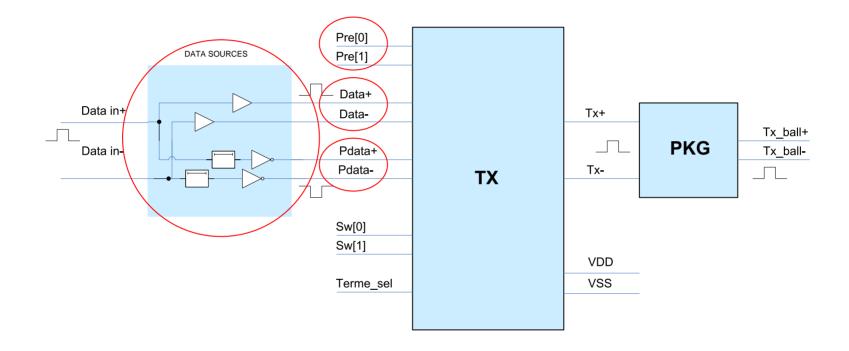

# Macromodeling of SERDES

The structure of transmitter device

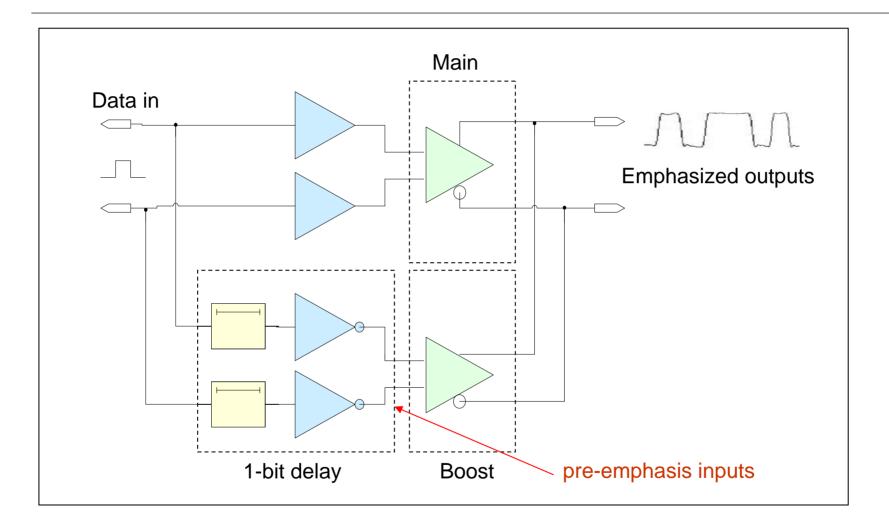

# Pre-emphasis

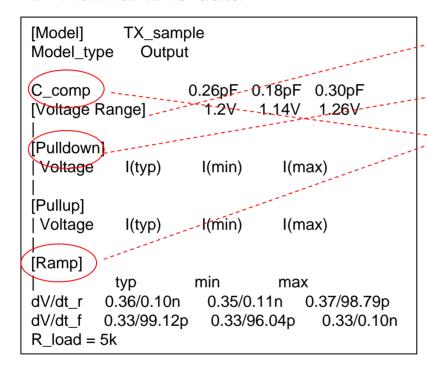

#### **Example Macromodel for Pre-emphasis**

#### V Normal IBIS data

#### Place in macromodel template

- → Ø (Pullup (ReferenceVoltage)

- Ø rt

- Ø (Pulldown (VICurve

- Ø (Ramp (dt

- Ø (C\_comp and/or padcap

#### Additional data

- Ø eqdb ---- Pre-emphasis db

- Scale ---- Vp-p

MGH MacroModel templates can be downloaded from

http://www.allegrosi.com

http://www.specctraquest.com

http://register.cadence.com/register.nsf/macromodeling?openform

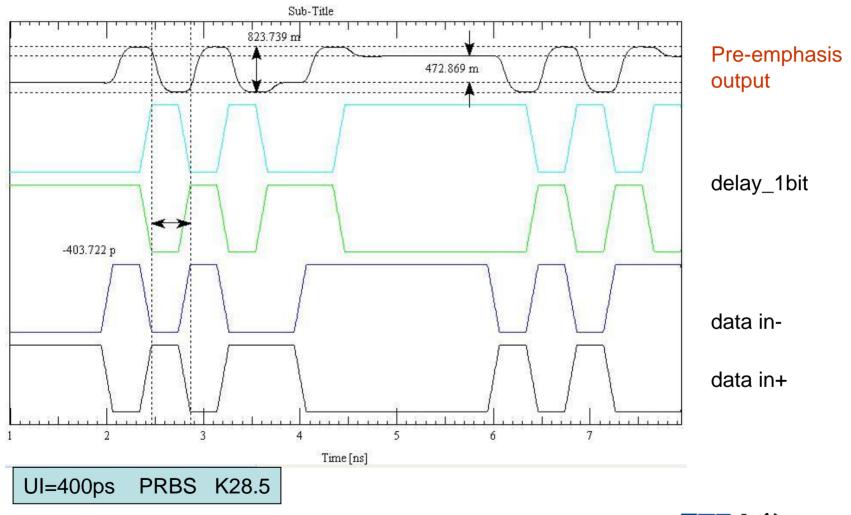

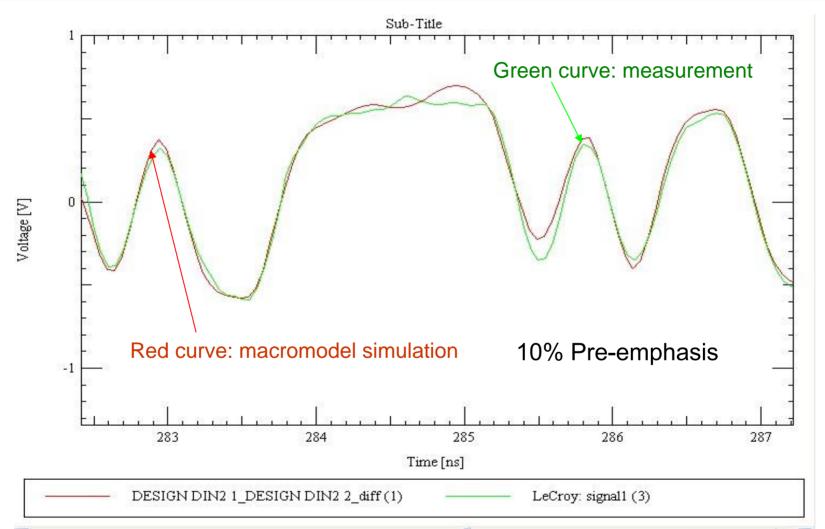

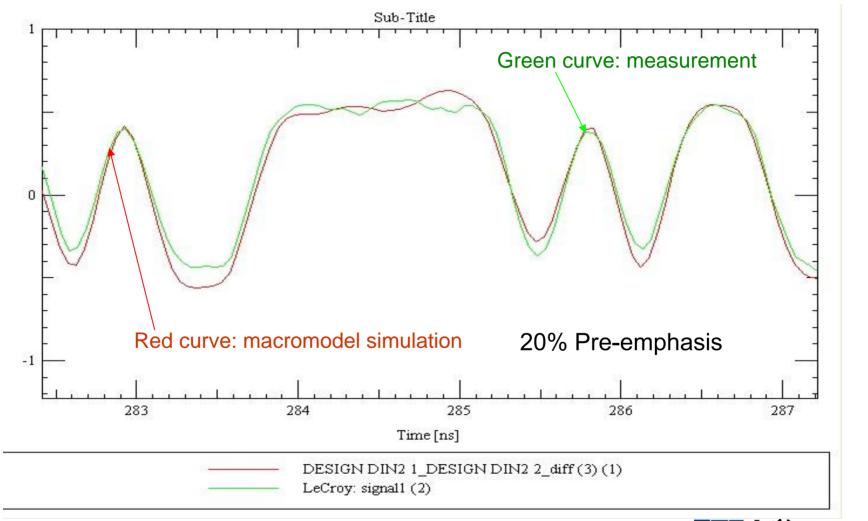

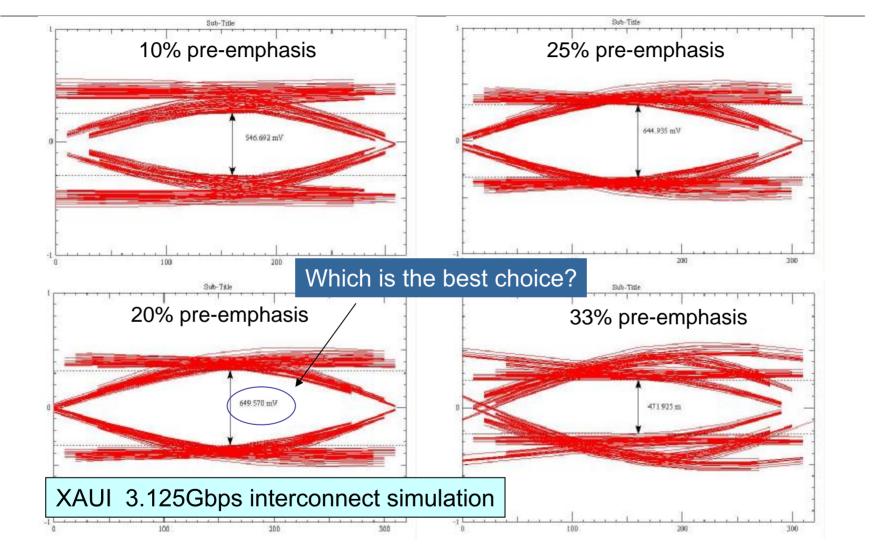

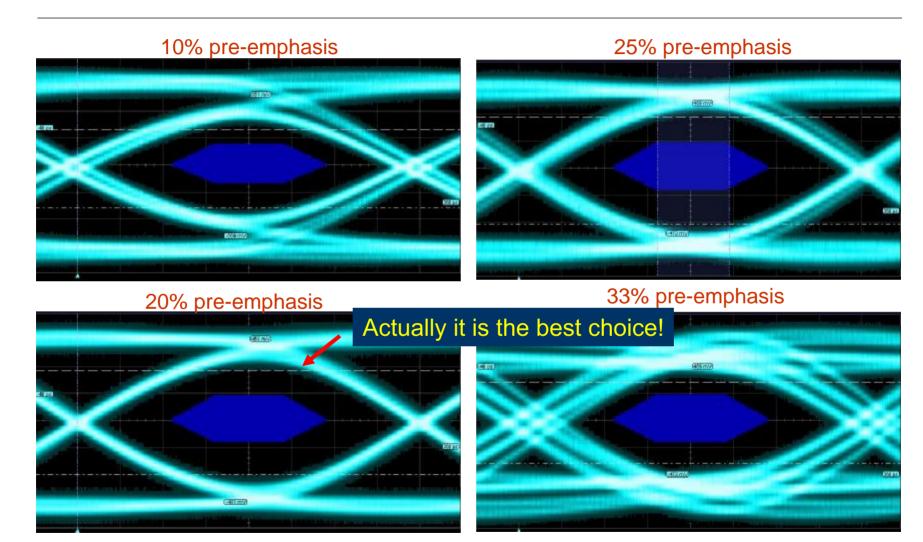

### Simulation of Pre-emphasis using marcormodel

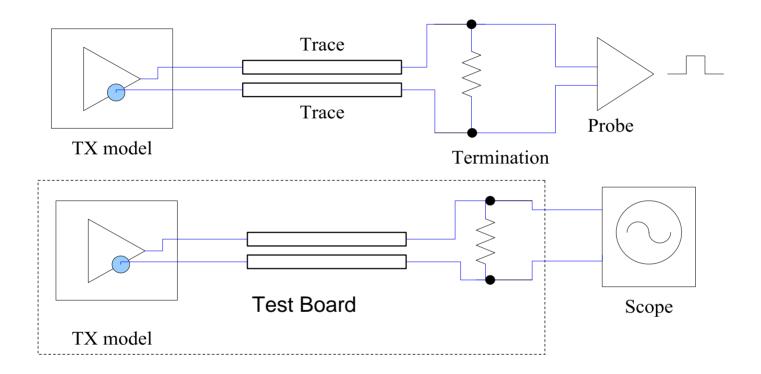

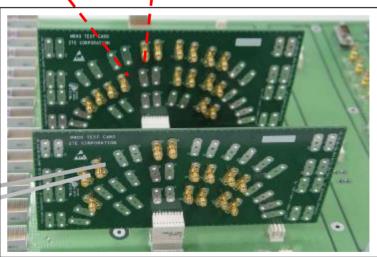

# Macromodel Validation setup

Correlations with lab measurements and HSPICE simulations

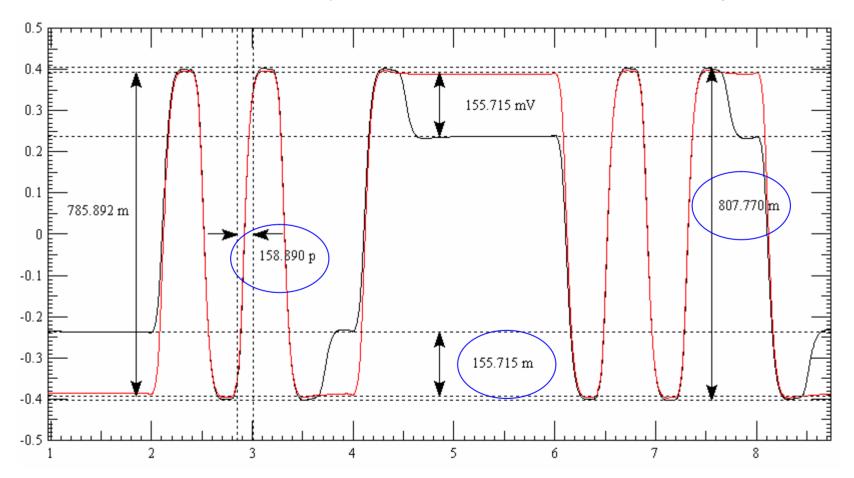

# Macromdeling simulation w./wo. pre-emphasis

Red Curve: No Pre-emphasis

Black Curve: 40% Pre-emphasis

#### Lab Correlation for Macromodels

- 1 Simulation using HSPICE models

- 2 Simulation using macrmodels

- 3 Correlate with laboratory measurement

#### Measurement versus Simulation

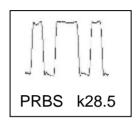

### Laboratory and measurement setup

The backplane has 10" of stripline

The daughter card has 3" of stripline

Data rate is 3.125Gb/s

#### Lab Correlation for Macromodels

#### Lab Correlation for Macromodels

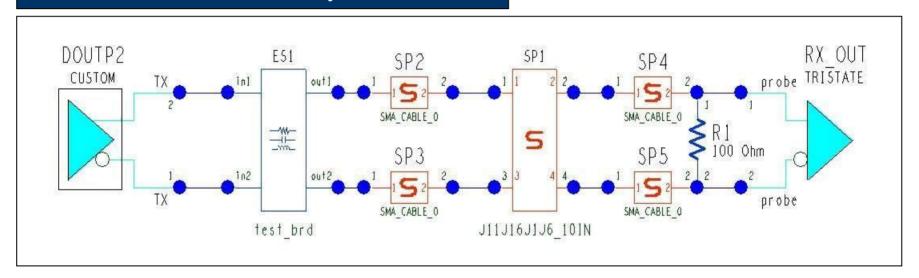

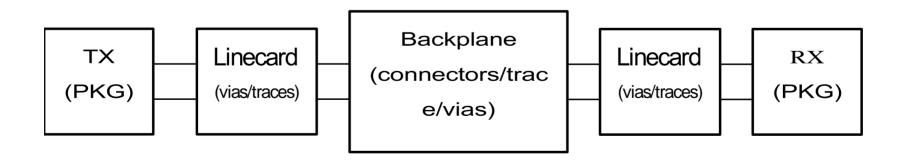

### Multi-GHz System Interconnect Simulation

- ▼ Multi-GHz System Interconnect Simulation includes:

- Transceiver Modeling

- Transceiver Package Modeling

- Interconnection (Traces, Vias, Connectors) Modeling

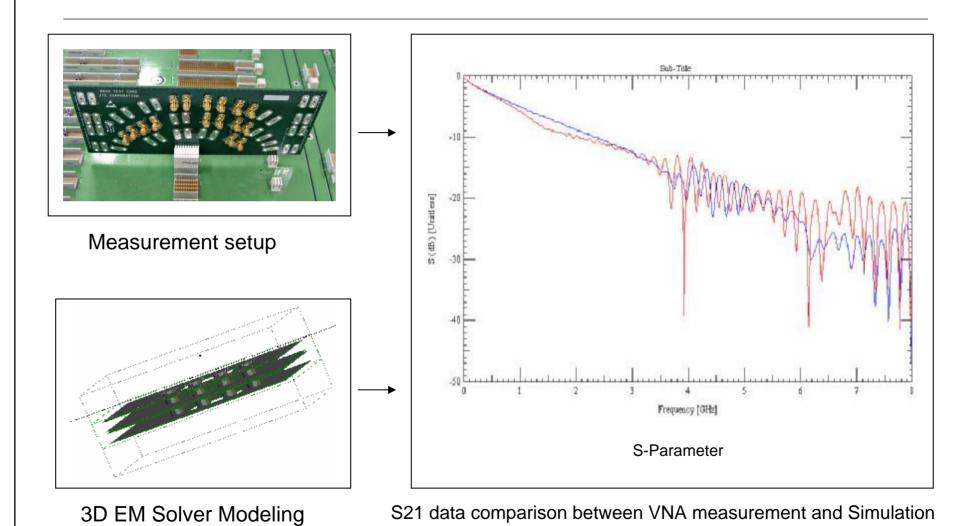

#### Multi-GHz System Interconnect Simulation

- Extracting models using 2D/3D EM solver

- Correlation based on VNA and TDR/TDT measurements

- SI/PI/EMC Simulations

- Eye diagram analysis and design margin budget

- Optimization

### Measurement modeling

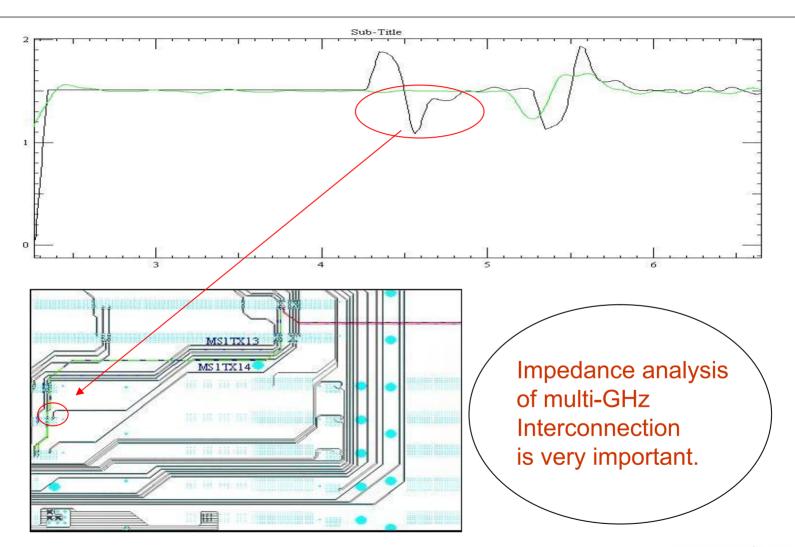

### **TDR** optimization

# Macromodel application

#### Correlation

2005-11-8

#### Conclusions

- Choose an appropriate modeling method is critical for simulation. Otherwise simulation may not be accurate enough or too complex and time consuming.

- Macromodel is an efficient solution for complex IO modeling, provided it be validated before usage.

- MacroModel enables much shorter simulation time than transistor-Level spice model. They can be used for system design and postlayout analysis.

- MacroModeling is appropriate for what-if analysis due to its relative short run time and sufficient accuracy.

- For multi-GHz Interconnection optimization, active device modeling using marcomodels, PCB modeling using EM solver, and correlation based on lab measurements have been proved to be very effective.